Ready for 25Gbps

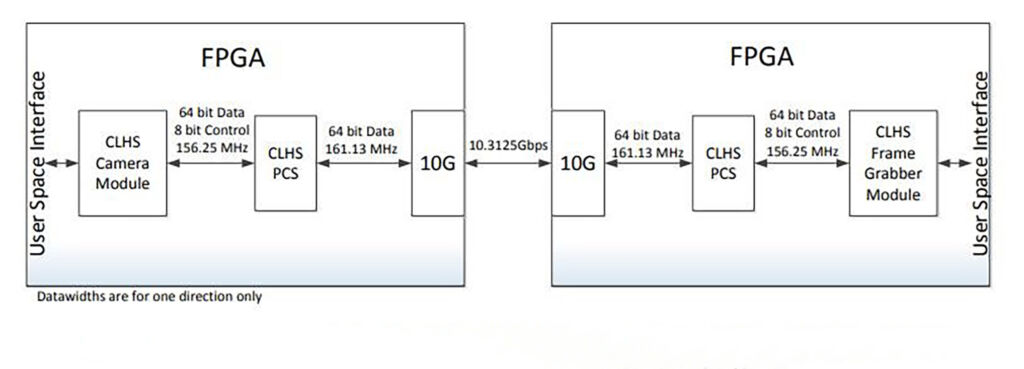

The well-designed IP core architecture makes CLHS ready without any modification to move to 25Gbps on an FPGA using 25Gbps transceivers over fiber with SFP28 or QSFP28 or MPO connectors. The soon-to-be-released specification revision will validate CLHS as having up to 100Gbps (4×25Gbps) available bandwidth using a single MPO connector. In achieving this speed increase, the CLHS X Protocol IP core remains completely unchanged. Therefore, all existing CLHS infrastructure also remains unchanged, making the move to 25Gbps inexpensive and straightforward for vendors and users. Contrast this with frame grabber interfaces that need to change core code and move to different line encoding to implement faster rates. Furthermore, CLHS has a very flexible and robust mechanism for changing the speed of the interface. Using MPO to LC, breakout cables, or SFP28 allows backward compatibility to existing CLHS 10Gbps frame grabbers or newly developed 25Gbps frame grabbers to support existing 10G cameras.

Getting to 50Gbps and Beyond

With FPGA and PHY technology ready to support 50Gbps and higher rates, CLHS is poised to deliver powerful real-time camera interfacing at even higher imaging rates. The features and capabilities already in place in the CLHS standard stand to make the path to 50Gbps effortless. The CLHS working group has leveraged the existing X Protocol IP core, adding a simple bridge from the 64bit output of the X Protocol IP core PCS to the 128bit input of 50Gbps FPGAs with built-in SerDes blocks. To achieve 50Gbps speeds, CLHS will introduce a virtual channel using a master and slave channel (or lane) all in one fiber. With this minor change in the specification, component vendors will be able to easily migrate to the higher-speed interfacing with minimal impact on hardware and software architecture.

Future of Frame Grabbers

The Camera Link HS standard is built for the future of imaging in its implementation of general IP cores, open-source VHDL, and inherent advanced line encoding and error correction. One key to future-proofing the standard is the seamless support for fiber cabling, something that may become standard in most imaging environments. Fiber cable is not fragile or more susceptible to bending, wrapping, or pinching than traditional copper wire. With current technologies, fiber is easy to work with and is field installable and modifiable. Able to carry more than twice the bandwidth of copper at distances of many kilometers, fiber is also less expensive than copper wire. Already a robust imaging interface, Camera Link HS continues to improve. Its use of 64b/66b encoding in 2012 still provides manufacturers and end users a long design cycle from 10Gbps all the way up to 50Gbps. The standard’s many features and capabilities make it stand out as a definitive choice in high-speed imaging applications both now and in the future.